Theoretical Paper

- Computer Organization

- Data Structure

- Digital Electronics

- Object Oriented Programming

- Discrete Mathematics

- Graph Theory

- Operating Systems

- Software Engineering

- Computer Graphics

- Database Management System

- Operation Research

- Computer Networking

- Image Processing

- Internet Technologies

- Micro Processor

- E-Commerce & ERP

Practical Paper

Industrial Training

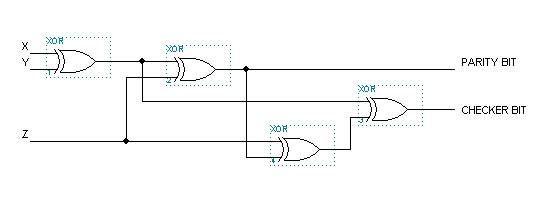

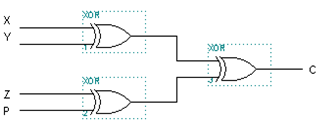

Parity bit Generator/checker

An even parity bit generator generates an output of 0 if the number of 1’s in the input sequence is even and 1 if the number of 1’s in the input sequence is odd. The checker circuit gives an output of 0 if there is no error in the parity bit generated. Thus it basically checks to see if the parity bit generator is error free or not.

Schematic:

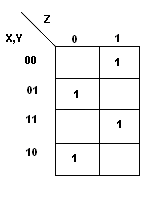

The design procedure is made simple by writing the truth table for the circuit.

Truth table:

Message Even parity bit Checker bit

| X Y Z | P | C |

| 000 | 0 | 0 |

| 001 | 1 | 0 |

| 010 | 1 | 0 |

| 011 | 0 | 0 |

| 100 | 1 | 0 |

| 101 | 0 | 0 |

| 101 | 0 | 0 |

| 111 | 1 | 0 |

The circuit can now be derived by drawing the K-map for the output.

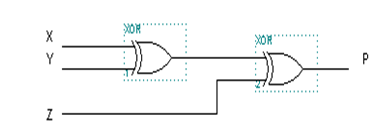

From this the minimal output equation is This function can be implemented using exclusive-or gates. The schematic of the parity generator circuit is shown

Similarly the checker circuit can be designed using XOR gates, where and the circuit is shown

Now the parity bit generator and the checker circuit can be combined into one circuit for simplicity. The final schematic of the circuit is shown