IAS Computer

General

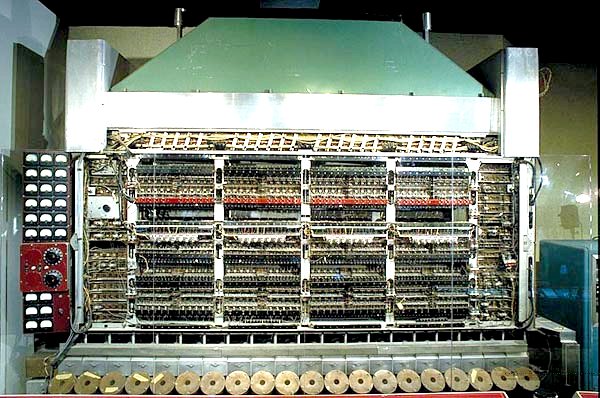

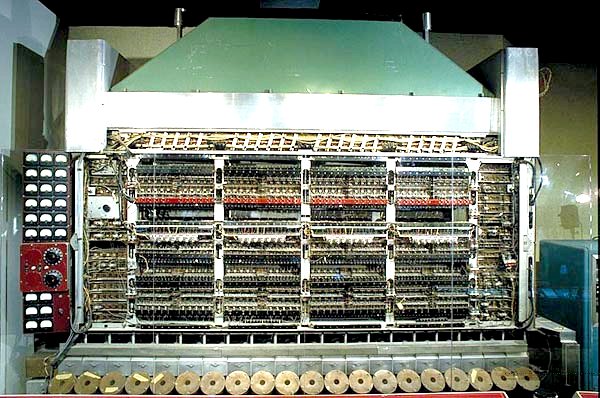

- The IAS computer was named for the Institute for Advanced Study in Princeton, N.J., where it was developed.

- Work on the IAS was begun in 1946 and completed in 1952.

Architecture

- The IAS computer was the first to store the program in the same memory as the data.

- The logic of the IAS machine was implemented with vacuum tubes.

- The memory of the IAS machine was implemented with cathode ray tubes.

- The word size is 40 bits.

- Memory is word addressed (not byte addressed.)

- Numbers were stored as fractions, not as integers.

- The distinction between fractions and integers only affects multiplication and division.

- Instructions are fixed size (20 bits), with a single address, stored 2 per word.

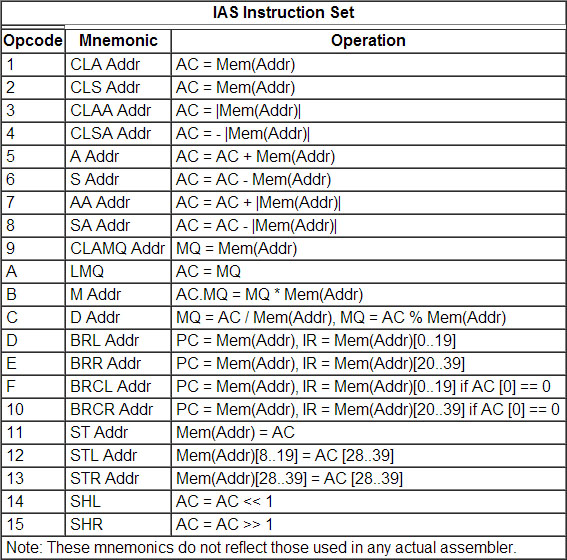

- 8 bits are allocated for the opcode, allowing 256 different operations; only 21 were implemented.

- 12 bits are allocated for the address, allowing a memory space of 4096 words; IAS was built with only 1024 words of memory.

Opcode |

Address |

Opcode |

Address |

- Two instructions are fetched at once.

- The IAS has 5 separate parts:

- CA, the Central Arithmetic part

- CC, the Central Control part

- M, the primary Memory part

- I, the Input part

- O, the Output part

- R is an external Recording medium.

- IAS has 7 registers, 2 of which can be addressed by instructions:

- Architectured Registers

- AC, the Accumulator (40 bits)

- MQ, the Multiplier/Quotient register (40 bits)

- Implemented Registers

- MDR, the Memory Data Register (40 bits)

- IBR, the Instruction Buffer Register (40 bits)

- IR, the Instruction Register (20 bits)

- PC, the Program Counter (12 bits)

- MAR, the Memory Address Register (12 bits)

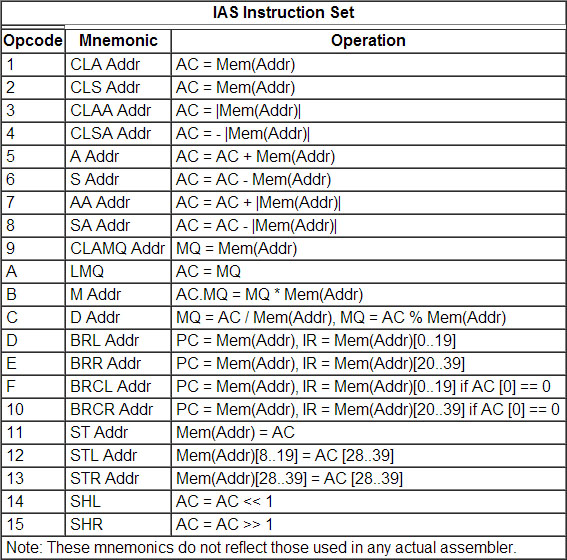

Instruction Set